# **Atmel 8051 Microcontrollers Hardware Manual**

# **Table of Contents**

| Sec | tion 1 | 1                                      |       |

|-----|--------|----------------------------------------|-------|

| The | 8051   | Instruction Set                        | 1-2   |

|     | 1.1    | Program Status Word                    | 1-2   |

|     | 1.2    | Addressing Modes                       | 1-3   |

|     | 1.3    | Arithmetic Instructions                |       |

|     | 1.4    | Logical Instructions                   | 1-6   |

|     | 1.5    | Data Transfers                         | 1-7   |

|     | 1.6    | External RAM                           | 1-10  |

|     | 1.7    | Lookup Tables                          | 1-10  |

|     | 1.8    | Boolean Instructions                   | 1-11  |

|     | 1.9    | Jump Instructions                      | 1-13  |

|     | 1.10   | Read-Modify-Write Instruction Features | 1-15  |

|     | 1.11   | Instruction Set Summary                | 1-16  |

|     | 1.12   | Instructions That Affect Flag Settings | 1-20  |

|     | 1.13   | Instruction Table                      | 1-21  |

|     | 1.14   | Instruction Definitions                | 1-24  |

| Sec | tion 2 | 2                                      |       |

| Com | mon    | Features Description                   | 2-66  |

|     | 2.1    | Introduction                           |       |

|     | 2.2    | Special Function Registers             |       |

|     | 2.3    | Oscillator and Clock Circuit           |       |

|     | 2.4    | CPU Timing                             | 2-71  |

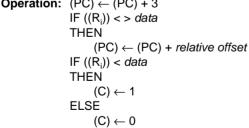

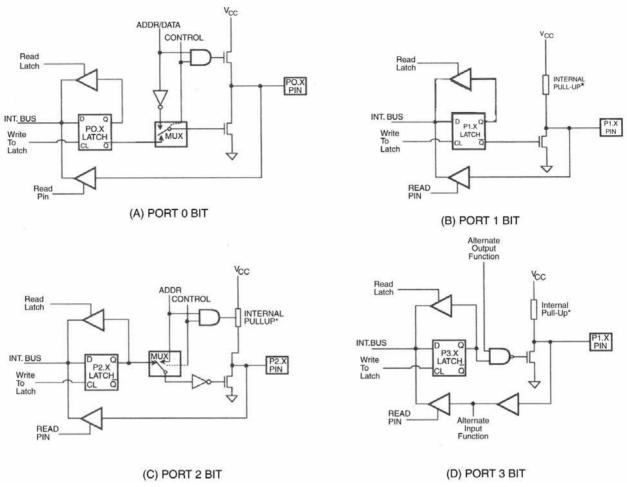

|     | 2.5    | Port Structures and Operation          |       |

|     | 2.6    | Accessing External Memory              |       |

|     | 2.7    | PSEN                                   |       |

|     | 2.8    | ALE                                    | 2-79  |

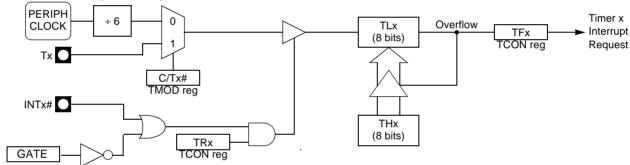

|     | 2.9    | Timer/Counters                         | 2-81  |

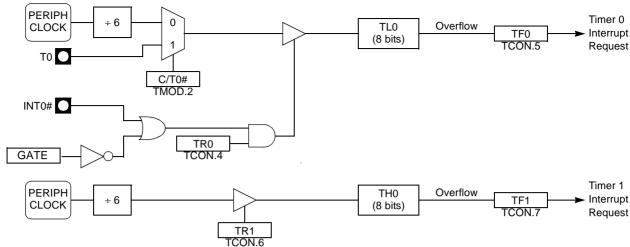

|     | 2.10   | Timer 0                                | 2-82  |

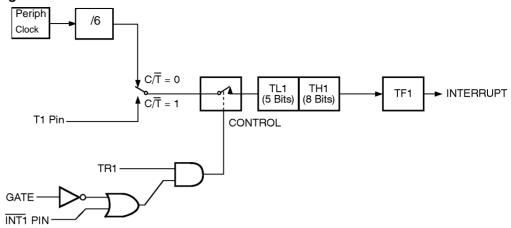

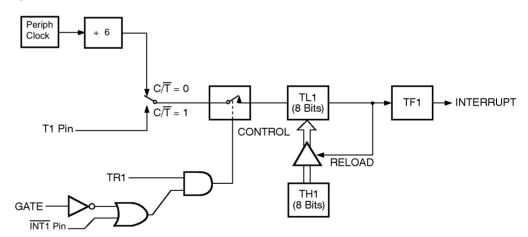

|     | 2.11   | Timer 1                                | 2-84  |

|     | 2.12   | Timer 2                                |       |

|     | 2.13   | Serial Interface                       | 2-94  |

|     | 2.14   | Framing Error Detection                | 2-104 |

|     |        | Automatic Address Recognition          |       |

|     | 2.16   | Interrupts                             | 2-112 |

# **Section 1**

# The 8051 Instruction Set

The 8051 instruction set is optimized for 8-bit control applications. It provides a variety of fast addressing modes for accessing the internal RAM to facilitate byte operations on small data structures. The instruction set provides extensive support for one-bit variables as a separate data type, allowing direct bit manipulation in control and logic systems that require Boolean processing.

An overview of the 8051 instruction set is presented below, with a brief description of how certain instructions might be used.

# 1.1 Program Status Word

The Program Status Word (PSW) contains several status bits that reflect the current state of the CPU. The PSW, shown in Table 1-1 on page 3, resides in SFR space. It contains the Carry bit, the Auxiliary Carry (for BCD operations), the two register bank select bits, the Overflow flag, a parity bit, and two user-definable status flags.

The Carry bit, other than serving the functions of a Carry bit in arithmetic operations, also serves as the "Accumulator" for a number of Boolean operations.

The bits RS0 and RS1 are used to select one of the four register banks shown below.

A number of instructions refer to these RAM locations as R0 through R7. The selection of which of the four banks is being referred to is made on the basis of the bits RS0 and RS1 at execution time.

The parity bit reflects the number of 1's in the Accumulator: P = 1 if the Accumulator contains an odd number of 1's, and P = 0 if the Accumulator contains an even number of 1's. Thus the number of 1's in the Accumulator plus P is always even.

Two bits in the PSW are uncommitted and may be used as general purpose status flags.

The PSW register contains program status information as detailed in Table 1-1.

Table 1-1. PSW: Program Status Word Register

|   | (MSB) |    |    |     |     |    |   | (LSB) |

|---|-------|----|----|-----|-----|----|---|-------|

| Ī | CY    | AC | F0 | RS1 | RS0 | OV | - | Р     |

| Symbol | Position | Name and Significance                                                                                                                            |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| CY     | PSW.7    | Carry flag                                                                                                                                       |

| AC     | PSW.6    | Auxiliary Carry flag.<br>(For BCD operations.)                                                                                                   |

| F0     | PSW.5    | Flag 0 (Available to the user for general purposes.)                                                                                             |

| RS1    | PSW.4    | Register bank Select control bits 1 & 0. Set/cleared by software to determine working register bank (see Note).                                  |

| RS0    | PSW.3    |                                                                                                                                                  |

| OV     | PSW.2    | Overflow flag.                                                                                                                                   |

| -      | PSW.1    | (reserved)                                                                                                                                       |

| Р      | PSW.0    | Parity flag. Set/cleared by hardware each instruction cycle to indicate and odd/even number of "one" bits in the accumulator, i.e., even parity. |

#### Note:

The contents of (RS1, RS0) enable the working register banks as follows:

(0.0)-Bank 0(00H-07H)

(0.1)-Bank 1(08H-0FH)

(1.0)-Bank 2(10H-17H)

(1.1)-Bank 3(18H-1FH)

# 1.2 Addressing Modes

The addressing modes in the 8051 instruction set are as follows:

# 1.2.1 Direct Addressing

In direct addressing the operand is specified by an 8-bit address field in the instruction. Only 128 Lowest bytes of internal Data RAM and SFRs can be directly addressed.

# 1.2.2 Indirect Addressing

In indirect addressing the instruction specifies a register which contains the address of the operand. Both internal and external RAM can be indirectly addressed.

The address register for 8-bit addresses can be R0 or R1 of the selected register bank, or the Stack Pointer. The address register for 16-bit addresses can only be the 16-bit "data pointer" register, DPTR.

# 1.2.3 Register

The register banks, containing registers R0 through R7, can be accessed by certain instructions which carry a 3-bit register specification within the opcode of the instruction. Instructions that access the registers this way are code efficient, since this mode eliminates an address byte. When the instruction is executed, one of the eight registers in the selected bank is accessed. One of four banks is selected at execution time by the two bank select bits in the PSW.

# 1.2.4 Register-specific Instructions

Some instructions are specific to a certain register. For example, some instructions always operate on the Accumulator, or Data Pointer, etc., so no address byte is needed to point to it. The opcode does this itself. Instructions that refer to the Accumulator as 'A' assemble as accumulator-specific opcodes.

# 1.2.5 Immediate Constants

The value of a constant can follow the opcode in Program Memory. For example;

MOV A, # 100

loads the Accumulator with the decimal number 100. The same number could be specified in hex digits as 64H.

### 1.2.6 Indexed Addressing

Only Program Memory can be accessed with indexed addressing, and it can only be read. This addressing mode is intended for reading look-up tables in Program Memory. A 16-bit base register (either DPTR or the Program Counter) points to the base of the table, and the Accumulator is set up with the table entry number. The address of the table entry in Program Memory is formed by adding the Accumulator data to the base pointer.

Another type of indexed addressing is used in the "case jump" instruction. In this case the destination address of a jump instruction is computed as the sum of the base pointer and the Accumulator data.

# 1.3 Arithmetic Instructions

The menu of arithmetic instructions is listed in Table 1-2. The table indicates the addressing modes that can be used with each instruction to access the <br/>byte> operand. For example, the ADD A, <byte> instruction can be written as:

```

ADD A,7FH (direct addressing)

ADD A,@ R0(indirect addressing)

ADD A,R7 (register addressing)

ADD A,# 127(immediate constant)

```

**Table 1-2.** A list of the Atmel 8051 Arithmetic Instructions.

| Mnemonic                                | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A                | ddressi | ng Mod | es      | Execution Time in X1<br>Mode<br>@12 MHz (µs) |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------|--------|---------|----------------------------------------------|

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Dir              | Ind     | Reg    | lm<br>m |                                              |

| ADD A, <byt>e</byt>                     | A = A + <byte></byte>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Х                | Χ       | Х      | Х       |                                              |

| ADDC A,<br><br><br><br><br><br><br><br> | A = A + <byte> + C</byte>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | х                | х       | x      | x       | 1                                            |

| SUBB A,<br><byte></byte>                | A = A - <byte> - C</byte>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | х                | х       | х      | х       | 1                                            |

| INC A                                   | A = A + 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Accur            | mulator | only   |         | 1                                            |

| INC <byte></byte>                       | <br><br><br><br><br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Х                | Х       | Х      |         | 1                                            |

| INC DPTR                                | DPTR = DPTR + 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Data             | Pointer | only   |         | 2                                            |

| DEC A                                   | A = A - 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Accur            | mulator | only   |         | 1                                            |

| DEC <byte></byte>                       | <br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br> | Х                | Х       | Х      |         | 1                                            |

| MUL AB                                  | $B:A = B \times A$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ACC              | and B o | nly    |         | 4                                            |

| DIV AB $A = Int [A/B]$ $B = Mod [A/B]$  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ACC and B only   |         |        | 4       |                                              |

| DA A Decimal Adjust                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Accumulator only |         |        | 1       |                                              |

The execution times listed in Table 1-2 assume a 12 MHz clock frequency and X1 mode. All of the arithmetic instructions execute in 1  $\mu$ s except the INC DPTR instruction, which takes 2  $\mu$ s, and the Multiply and Divide instructions, which take 4  $\mu$ s.

Note that any byte in the internal Data Memory space can be incremented or decremented without going through the Accumulator.

One of the INC instructions operates on the 16-bit Data Pointer. The Data Pointer is used to generate 16-bit addresses for external memory, so being able to increment it in one 16-bit operation is a useful feature.

The MUL AB instruction multiplies the Accumulator by the data in the B register and puts the 16-bit product into the concatenated B and Accumulator registers.

The DIV AB instruction divides the Accumulator by the data in the B register and leaves the 8-bit quotient in the Accumulator, and the 8-bit remainder in the B register.

Oddly enough, DIV AB finds less use in arithmetic "divide" routines than in radix conversions and programmable shift operations. An example of the use of DIV AB in a radix conversion will be given later. In shift operations, dividing a number by  $2^n$  shifts its n bits to the right. Using DIV AB to perform the division completes the shift in 4  $\mu$ s leaves the B register holding the bits that were shifted out.

The DA A instruction is for BCD arithmetic operations. In BCD arithmetic ADD and ADDC instructions should always be followed by a DA A operation, to ensure that the result is also in BCD. Note that DAA will not convert a binary number to BCD. The DA A operation produces a meaningful result only as the second step in the addition of two BCD bytes.

# 1.4 Logical Instructions

Table 1-3 shows the list of logical instructions. The instructions that perform Boolean operations (AND, OR, Exclusive OR, NOT) on bytes perform the operation on a bit-by-bit basis. That is, if the Accumulator contains 00110101B and <br/>

<a href="https://doi.org/10.2016/j.jps.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.contains-notation.cont

```

ANL A, <byte>

```

will leave the Accumulator holding 00010001B.

The addressing modes that can be used to access the <byte> operand are listed in Table 1-3. Thus, the ANL A, <byte> instruction may take any of the following forms.

```

ANL A, 7FH(direct addressing)

ANL A, @ R1(indirect addressing)

ANL A, R6(register addressing)

ANL A, # 53H(immediate constant)

```

All of the logical instructions that are Accumulator specific execute in 1  $\mu$ s (using a 12 MHz clock and X1 mode). The others take 2  $\mu$ s.

**Table 1-3.** A list of the Atmel 8051 Logical Instructions

| Mnemonic                  | Operation                                    | Ad               | ddressi          | ng Mod   | es  | Execution Time<br>@ 12MHz (µs) |

|---------------------------|----------------------------------------------|------------------|------------------|----------|-----|--------------------------------|

|                           |                                              | Dir              | Ind              | Reg      | lmm |                                |

| ANL A, <byte></byte>      | A = A AND <byte></byte>                      | Х                | Х                | Х        | Х   | 1                              |

| ANL <byte>, A</byte>      | <br><byte> = <byte> AND A</byte></byte>      | Х                |                  |          |     | 1                              |

| ANL <byte>, # data</byte> | <br><byte> = <byte> AND # data</byte></byte> | Х                |                  |          |     | 2                              |

| ORL A, <byte></byte>      | A = A OR <byte></byte>                       | Х                | Х                | Х        | Х   | 1                              |

| ORL <byte>, A</byte>      | <br><byte> = <byte> OR A</byte></byte>       | Х                |                  |          |     | 1                              |

| ORL <byte>, # data</byte> | <br><byte> = <byte> OR # data</byte></byte>  | х                |                  |          |     | 2                              |

| XRL A, <byte></byte>      | A = A XOR <byte></byte>                      | Х                | Х                | Х        | Х   | 1                              |

| XRL <byte>, A</byte>      | <br><byte> = <byte> XOR A</byte></byte>      | Х                |                  |          |     | 1                              |

| XRL <byte>, # data</byte> | <br><byte> = <byte> XOR # data</byte></byte> | х                |                  |          |     | 2                              |

| CLR A                     | A = 00H                                      | ,                | Accumu           | lator on | ly  | 1                              |

| CLP A                     | A = NOT A                                    | ,                | Accumu           | lator on | ly  | 1                              |

| RL A                      | Rotate ACC Left 1 bit                        | ,                | Accumulator only |          | 1   |                                |

| RLC A                     | Rotate Left through Carry                    | Accumulator only |                  | 1        |     |                                |

| RR A                      | Rotate ACC Right 1 bit                       | Accumulator only |                  | 1        |     |                                |

| RRC A                     | Rotate Right through Carry                   | Accumulator only |                  | 1        |     |                                |

| SWAP A                    | Swap Nibbles in A                            | ,                | Accumu           | lator on | ly  | 1                              |

Note that Boolean operations can be performed on any byte in the internal Data Memory space without going through the Accumulator. The XRL <byte>, # data instruction, for example, offers a quick and easy way to invert port bits, as in

```

XRL P1, #OFFH

```

If the operation is in response to an interrupt, not using the Accumulator saves the time and effort to stack it in the service routine.

The Rotate instructions (RL A, RLC A, etc.) shift the Accumulator 1 bit to the left or right. For a left rotation, the MSB rolls into the LSB position. For a right rotation, the LSB rolls into the MSB position.

The SWAP A instruction interchanges the high and low nibbles within the Accumulator. this is a useful operation in BCD manipulations. For example, if the Accumulator contains a binary number which is known to be less than 100, it can be quickly converted to BCD by the following code:

```

MOV B, #10

DIV AB

SWAP A

ADD A,B

```

Dividing the number by 10 leaves the tens digit in the low nibble of the Accumulator, and the ones digit in the B register. The SWAP and ADD instructions move the tens digit to the high nibble of the Accumulator, and the ones digit to the low nibble.

### 1.5 Data Transfers

### 1.5.1 Internal RAM

Table 1-4 shows the menu of instructions that are available for moving data around within the internal memory spaces, and the addressing modes that can be used with each one. With a 12 MHz clock and X1 mode, all of these instructions execute in either 1 or  $2\,\mu s$ .

The MOV <dest>, <src> instruction allows data to be transferred between any two internal RAM or SFR locations without going through the Accumulator. Remember the Upper 128 bytes of data RAM can be accessed only by indirect, and SFR space only by direct addressing.

Note that in all 8051 devices, the stack resides in on-chip RAM, and grows upwards. The PUSH instruction first increments the Stack Pointer (SP), then copies the byte into the stack. PUSH and POP use only direct addressing to identify the byte being saved or restored, but the stack itself is accessed by indirect addressing using the SP register.

This means the stack can go into the Upper 128, if they are implemented, but not into SFR space.

**Table 1-4.** Atmel 8051 Data Transfer Instructions that Access Internal Data Memory Space

| Mnemonic                           | Operation                           | А   | ddressi | ng Mode | es  | Execution Time<br>@ 12MHz (µs) |

|------------------------------------|-------------------------------------|-----|---------|---------|-----|--------------------------------|

|                                    |                                     | Dir | Ind     | Reg     | lmm |                                |

| MOV A, <src></src>                 | A = <src></src>                     | Х   | Х       | Х       | Х   | 1                              |

| MOV <dest>, A</dest>               | <dest> = A</dest>                   | Х   | Х       | Х       |     | 1                              |

| MOV <dest>,<br/><src></src></dest> | <dest> = <src></src></dest>         | Х   | х       | х       | Х   | 2                              |

| MOV DPTR, #<br>data 16             | DPTR = 16-bit immediate constant    |     |         |         | х   | 2                              |

| PUSH <src></src>                   | INC SP: MOV "@SP", <scr></scr>      | Х   |         |         |     | 2                              |

| POP <dest></dest>                  | MOV <dest>, "@SP": DEC SP</dest>    | Х   |         |         |     | 2                              |

| XCH A, <byte></byte>               | ACC and <byte> Exchange Data</byte> | Х   | Х       | Х       |     | 1                              |

| XCHD A, @Ri                        | ACC and @ Ri exchange low nibbles   |     | х       |         |     | 1                              |

The Upper 128 are not implemented in the 8 standard 8051, nor in their ROMless. With these devices, if the SP points to the Upper 128 PUSHed bytes are lost, and POPped bytes are indeterminate.

The Data Transfer instructions include a 16-bit MOV that can be used to initialize the Data Pointer (DPTR) for look-up tables in Program Memory, or for 16-bit external Data Memory accesses.

The XCH A, <byte> instruction causes the Accumulator and addressed byte to exchange data.

The XCHD A, @ Ri instruction is similar, but only the low nibbles are involved in the exchange.

The see how XCH and XCHD can be used to facilitate data manipulations, consider first the problem of shifting an 8-digit BCD number two digits to the right. Table 1-5 shows how this can be done using direct MOVs, and for comparison how it can be done using XCH instructions. To aid in understanding how the code works, the contents of the registers that are holding the BCD number and the content of the Accumulator are shown alongside each instruction to indicate their status after the instruction has been executed.

After the routine has been executed, the Accumulator contains the two digits that were shifted out on the right. Performing the routine with direct MOVs uses 14 code bytes and 9  $\mu s$  of execution time (assuming a 12 MHz clock and X1 mode). The same operation with XCHs uses less code and executes almost twice as fast.

Table 1-5. Shifting a BCD Number Two Digits to the Right

|                                 | 2A         | 2B | 2C | 2D | 2E | ACC |

|---------------------------------|------------|----|----|----|----|-----|

| MOV A,2EH                       | 00         | 12 | 34 | 56 | 78 | 78  |

| MOV 2EH, 2DH                    | 00         | 12 | 34 | 56 | 56 | 78  |

| MOV 2DH, 2CH                    | 00         | 12 | 34 | 34 | 56 | 78  |

| MOV 2CH, 2BH                    | 00         | 12 | 12 | 34 | 56 | 78  |

| MOV 2BH, # 0                    | 00         | 00 | 12 | 34 | 56 | 78  |

| Note: Using direct MOVs: 14     | bytes, 9 μ | S  |    |    |    |     |

|                                 | 2A         | 2B | 2C | 2E | 2E | ACC |

| CLR A                           | 00         | 12 | 34 | 56 | 78 | 00  |

| XCH A,2BH                       | 00         | 00 | 34 | 56 | 78 | 12  |

| XCH A,2CH                       | 00         | 00 | 12 | 56 | 78 | 34  |

| XCH A,2DH                       | 00         | 00 | 12 | 34 | 78 | 56  |

| XCH A,2EH                       | 00         | 00 | 12 | 34 | 56 | 78  |

| Note: Using XCHs: 9 bytes, 5 μs |            |    |    |    |    |     |

Table 1-6. Shifting a BCD Number One Digit to the Right

|                     | 2A | 2B | 2C | 2D | 2E | ACC |

|---------------------|----|----|----|----|----|-----|

| MOV R1,# 2EH        | 00 | 12 | 34 | 56 | 78 | XX  |

| MOV R0, # 2DH       | 00 | 12 | 34 | 56 | 78 | XX  |

| loop for R1 = 2EH:  |    |    |    |    |    |     |

| LOOP: MOV A, @R1    | 00 | 12 | 34 | 56 | 78 | 78  |

| XCHD A, @R0         | 00 | 12 | 34 | 58 | 78 | 76  |

| SWAP A              | 00 | 12 | 34 | 58 | 78 | 67  |

| MOV @R1, A          | 00 | 12 | 34 | 58 | 67 | 67  |

| DEC R1              | 00 | 12 | 34 | 58 | 67 | 67  |

| DEC R0              | 00 | 12 | 34 | 58 | 67 | 67  |

| CJNE R1, #2AH, LOOP |    |    |    |    |    |     |

| loop for R1 = 2DH:  | 00 | 12 | 38 | 45 | 67 | 45  |

| loop for R1 = 2CH:  | 00 | 18 | 23 | 45 | 67 | 23  |

| loop for R1 = 2BH:  | 08 | 01 | 23 | 45 | 67 | 01  |

|                     |    |    |    |    |    |     |

| CLR A               | 08 | 01 | 23 | 45 | 67 | 00  |

| XCH A,2AH           | 00 | 01 | 23 | 45 | 67 | 08  |

To right-shift by an odd number of digits, a one-digit shift must be executed. Table 1-6 shows a sample of code that will right-shift a BCD number one digit, using the XCHD instruction. Again, the contents of the registers holding the number and of the Accumulator are shown alongside each instruction.

First, pointers R1 and R0 are set up to point to the two bytes containing the last four BCD digits. Then a loop is executed which leaves the last byte, location 2EH, holding the last two digits of the shifted number. The pointers are decremented, and the loop is

repeated for location 2DH. The CJNE instruction (Compare and Jump if Not Equal) is a loop control that will be described later.

The loop is executed from LOOP to CJNE for R1 = 2EH, 2DH, 2CH and 2BH. At that point the digit that was originally shifted out on the right has propagated to location 2AH. Since that location should be left with 0s, the lost digit is moved to the Accumulator.

### 1.6 External RAM

Table 1-7 shows a list of the Data Transfer instructions that access external Data Memory. Only indirect addressing can be used. The choice is whether to use a one-byte address, @Ri, where Ri can be either R0 or R1 of the selected register bank, or a two-byte address, @DPTR. The disadvantage to using 16-bit addresses if only a few Kbytes of external RAM are involved is that 16-bit addresses use all 8 bits of Port 2 as address bus. On the other hand, 8-bit addresses allow one to address a few Kbytes of RAM, as shown in Table 1-7, without having to sacrifice all of Port 2.

All of these instructions execute in 2 μs, with a 12 MHz clock (and X1 mode).

Note that in all external Data RAM accesses, the Accumulator is always either the destination or source of the data.

The read and write strobes to external RAM are activated only during the execution of a MOVX instruction. Separately these signals are inactive, and in fact if they're not going to be used at all, their pins are available as extra I/O lines.

| Address Width | Mnemonic       | Operation                    | Execution Time<br>@ 12MHz (µs) |

|---------------|----------------|------------------------------|--------------------------------|

| 8 bits        | MOVX A, @Ri    | Read external<br>RAM @ Ri    | 2                              |

| 8 bits        | MOVX @ Ri, A   | Write external<br>RAM @ Ri   | 2                              |

| 16 bits       | MOVX A, @ DPTR | Read external<br>RAM @ DPTR  | 2                              |

| 16 bits       | MOVX @ DPTR, A | Write external<br>RAM @ DPTR | 2                              |

Table 1-7. Data Transfer Instructions that Access External Data Memory Space

# 1.7 Lookup Tables

Table 1-8 shows the two instructions that are available for reading lookup tables in Program Memory. Since these instructions access only Program Memory, the lookup tables can be read, not updated. The mnemonic is MOVC for "move constant".

If the table access is to external Program Memory, then the read strobe is PSEN.

The first MOVC instruction in Table 1-8 can accommodate a table of up to 256 entries, numbered 0 through 255. The number of the desired entry is loaded into the Accumulator, and the Data Pointer is set up to point to beginning of the table. Then

copies the desired table entry into the Accumulator.

The other MOVC instruction works the same way, except the Program Counter (PC) is used as the table base, and the table is accessed through a subroutine. First the number of the desired entry is loaded into the Accumulator, and the subroutine is called:

MOV A, ENTRY\_NUMBER

The subroutine "TABLE" would look like this:

```

TABLE:MOVC A, @A + PC RET

```

The table itself immediately follows the RET (return) instruction in Program Memory. This type of table can have up to 255 entries, numbered 1 through 255. Number 0 cannot be used, because at the time the MOVC instruction is executed, the PC contains the address of the RET instruction. An entry numbered 0 would be the RET opcode itself.

Table 1-8. Lookup Table Read Instructions

| Mnemonic          | Operation                     | Execution Time<br>@ 12MHz (µs) |

|-------------------|-------------------------------|--------------------------------|

| MOVC A, @A + DPTR | Read Pgm Memory at (A + DPTR) | 2                              |

| MOVC A, @A + PC   | Read Pgm Memory at (A + PC)   | 2                              |

# 1.8 Boolean Instructions

8051 devices contain a complete Boolean (single-bit) processor. The internal RAM contains 128 addressable bits, and the SFR space can support up to 128 other addressable bits. All of the port lines are bit-addressable, and each one can be treated as a separate single-bit port. The instructions that access these bits are not just conditional branches, but a complete menu of move, set, clear, complement, OR and AND instructions. These kinds of bit operations are not easily obtained in other architectures with any amount of byte-oriented software.

The instruction set for the Boolean processor is shown in Table 1-9. All bit accesses are by direct addressing. Bit addresses 00H through 7FH are in the Lower 128, and bit addresses 80H through FFH are in SFR space.

Table 1-9. 8051 Boolean Instructions

| Mnemonic    | Operation                | Execution Time<br>@ 12MHz (µs) |

|-------------|--------------------------|--------------------------------|

| ANL C,bit   | C = C AND bit            | 2                              |

| ANL C,/bit  | C = C AND (NOT bit)      | 2                              |

| ORL C,bit   | C = C OR bit             | 2                              |

| ORL C,/bit  | C = C OR (NOT bit)       | 2                              |

| MOV C,bit   | C = bit                  | 1                              |

| MOV bit,C   | bit = C                  | 2                              |

| CLR C       | C = 0                    | 1                              |

| CLR bit     | bit = 0                  | 1                              |

| SETB C      | C = 1                    | 1                              |

| SETB bit    | bit = 1                  | 1                              |

| CPL C       | C = NOT C                | 1                              |

| CPL bit     | bit = NOT bit            | 1                              |

| JC rel      | Jump if $C = 1$          | 2                              |

| JNC rel     | Jump if $C = 0$          | 2                              |

| JB bit,rel  | Jump if bit = 1          | 2                              |

| JNB bit,rel | Jump if bit = 0          | 2                              |

| JBC bit,rel | Jump if bit = 1; CLR bit | 2                              |

Note how easily an internal flag can be moved to a port pin:

MOV C, FLAG MOV P1.0, C

In this example, FLAG is the name of any addressable bit in the lower 128 or SFR space. An I/O line (the LSB of Port 1, in the case) is set or cleared depending on whether the flag bit is 1 or 0.

The Carry bit in the PSW is used as the single-bit Accumulator of the Boolean processor. Bit instructions that refer to the Carry bit as C assemble as Carry-specific instructions (CLR C, etc.). The Carry bit also has a direct address, since it resides in the PSW register, which is bit-addressable.

Note that the Boolean instruction set includes ANL and ORL operations, but not the XRL (Exclusive OR) operation. An XRL operation is simple to implement in software. Suppose, for example, it is required to form the Exclusive OR of two bits:

C= bit1 XRL bit2

The software to do that could be as follows:

MOV C, bit1 JNB bit2, OVER CPL C OVER: (continue)

First, bit 1 is moved to the Carry. If bit 2 = 0, then C now contains the correct result. That is, bit 1 XRL bit2 = bit1 if bit2 = 0. On the other hand, if bit2 = 1 C now contains the complement of the correct result. It need only be inverted (CPL C) to complete the operation.

This code uses the JNB instruction, one of a series of bit-test instructions which execute a jump if the addressed bit is set (JC, JB, JBC) or if the addressed bit is not set (JNC, JNB). In the above case, bit2 is being tested, and if bit2 = 0 the CPL C instruction is jumped over.

JBC executes the jump if the addressed bit is set, and also clears the bit. Thus a flag can be tested and cleared in one operation.

All the PSW bits are directly addressable, so the Parity bit, or the general purpose flags, for example, are also available to the bit-test instructions.

### 1.8.1 Relative Offset

The destination address for these jumps is specified to the assembler by a label or by an actual address in Program Memory. However, the destination address assembles to a relative offset byte. This is a signed (two's complement) offset byte which is added to the PC in two's complement arithmetic if the jump is executed.

The range of the jump is therefore -128 to +127 Program Memory bytes relative to the first byte following the instruction.

Table 1-10. Addressing Modes

| R <sub>n</sub>  | Register R7-R0 of the currently selected Register Bank.                                                                                                                   |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| direct          | 8-bit internal data location's address. This could be an Internal Data RAM location (0-127) or a SFR [i.e., I/O port, control register, status register, etc. (128-255)]. |

| @R <sub>i</sub> | 8-bit internal data RAM location (0-255) addressed indirectly through register R1or R0.                                                                                   |

| #data           | 8-bit constant included in instruction.                                                                                                                                   |

| #data 16        | 16-bit constant included in instruction.                                                                                                                                  |

| addr 16         | 16-bit destination address. Used by LCALL and LJMP. A branch can be anywhere within the 64K byte Program Memory address space.                                            |

Table 1-10. Addressing Modes

| addr 11 | 11-bit destination address. Used by ACALL and AJMP. The branch will be within the same 2K byte page of program memory as the first byte of the following instruction. |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rel     | Signed (two's complement) 8-bit offset byte. Used by SJMP and all conditional jumps. Range is -128 to +127 bytes relative to first byte of the following instruction. |

| bit     | Direct Addressed bit in Internal Data RAM or Special Function Register.                                                                                               |

# 1.9 Jump Instructions

Table 1-11 shows the list of unconditional jumps.

**Table 1-11.** Unconditional Jumps in Atmel 8051

| Mnemonic      | Operation               | Execution Time @ 12MHz (µs) |

|---------------|-------------------------|-----------------------------|

| JMP addr      | Jump to addr            | 2                           |

| JMP @A + DPTR | Jump to A + DPTR        | 2                           |

| CALL addr     | Call subroutine at addr | 2                           |

| RET           | Return from subroutine  | 2                           |

| RETI          | Return from interrupt   | 2                           |

| NOP           | No operation            | 1                           |

The table lists a single "JMP addr" instruction, but in fact there are three -SJMP, LJMP, AJMP -which differ in the format of the destination address. JMP is a generic mnemonic which can be used if the programmer does not care how the jump is encoded.

The SJMP instruction encodes the destination address as relative offset, as described above. The instruction is 2 bytes long, consisting of the opcode and the relative offset byte. The jump distance is limited to range of -128 to + 127 bytes relative to the instruction following the SJMP.

The LJMP instruction encodes the destination address as a 16-bit constant. The instruction is 3 bytes long, consisting of the opcode and two address bytes. The destination address can be anywhere in the 64K Program Memory space.

The AJMP instruction encodes the destination address as an 11-bit constant. The instruction is 2 bytes long, consisting of the opcode, which itself contains 3 of the 11 address bits, followed by another byte containing the low 8 bits of the destination address. When the instruction is executed, these 11 bits are simply substituted for the low 11 bits in the PC. The high 5 bits stay the same. Hence the destination has to be within the same 2K block as the instruction following the AJMP.

In all cases the programmer specifies the destination address to the assembler in the same way: as a label or as a 16-bit constant. The assembler will put the destination address into the correct format for the given instruction. If the format required by the instruction will not support the distance to the specified destination address, a "Destination out of range" message is written, into the list file.

The JMP @ A + DPTR instruction supports case jumps. The destination address is computed at execution time as the sum of the 16-bit DPTR register and the Accumulator. Typically, DPTR is set up with the address of a jump table, and the Accumulator is given an index to the table. In a 5-way branch, for example, an integer 0 through 4 is loaded into the Accumulator.

The code to be executed might be as follows:

MOV DPTR, # JUMP\_TABLE

MOV A, INDEX\_NUMBER

RL A

JMP @ A + DPTR

The RLA instruction converts the index number (0 through 4) to an even number on the range 0 through 8, because each entry in the jump table is 2 bytes long:

```

JUMP_TABLE:

AJMP CASE_0

AJMP CASE_1

AJMP CASE_2

AJMP CASE_3

AJMP CASE_4

```

Table 1-11 shows a single "CALL addr" instruction, but there are two of them -LCALL and ACALL -which differ in the format in which the subroutine address is given to the CPU. CALL is a generic mnemonic which can be used if the programmer does not care which way the address is encoded.

The LCALL instruction uses the 16-bit address format, and the subroutine can be anywhere in the 64K Program Memory space. The ACALL instruction uses the 11-bit format, and the subroutine must be in the same 2K block as the instruction following the ACALL.

In any case the programmer specifies the subroutine address to the assembler in the same way: as a label or as a 16-bit constant. The assembler will put the address into the correct format for the given instructions.

Subroutines should end a RET instruction, which returns execution following the CALL.

RETI is used to return from an interrupt service routine. The only difference between RET and RETI is that RETI tells the interrupt control system that the interrupt in progress is done. If there is no interrupt in progress at the time RETI is executed, then the RETI is functionally identical to RET.

Table 1-12 shows the list of conditional jumps available to the Atmel 8051 user. All of these jumps specify the destination address by the relative offset method, and so are limited to a jump distance of -128 to + 127 bytes from the instruction following the conditional jump instruction. Important to note, however, the user specifies to the assembler the actual destination address the same way as the other jumps: as a label or a 16-bit constant.

| Mnemonic                     | Operation                      | А                  | ddress | ing Mode    | es  | Execution Time<br>@ 12MHz (µs) |

|------------------------------|--------------------------------|--------------------|--------|-------------|-----|--------------------------------|

|                              |                                | DIR                | IND    | REG         | IMM |                                |

| JZ rel                       | Jump if A = 0                  |                    | Accum  | ulator only | /   | 2                              |

| JNZ rel                      | Jump if A ≠ 0                  | Accumulator only 2 |        |             | 2   |                                |

| DJNZ <byte>,rel</byte>       | Decrement and jump if not zero | Х                  |        | Х           |     | 2                              |

| CJNZ A, <byte>,rel</byte>    | Jump if A = <byte></byte>      | Х                  |        |             | Х   | 2                              |

| CJNE <byte>,#data,rel</byte> | Jump if <byte> = #data</byte>  |                    | Х      | Х           |     | 2                              |

Table 1-12. Conditional Jumps in Atmel 8051 Devices

There is no Zero bit in the PSW. The JZ and JNZ instructions test the Accumulator data for that condition.

The DJNZ instruction (Decrement and Jump if Not Zero) is for loop control. To execute a loop N times, load a counter byte with N and terminate the loop with DJNZ to the beginning of the loop, as shown below for N = 10:

\*

(end loop)

DJNZ COUNTER, LOOP

(continue)

The CJNE instruction (Compare and Jump if Not Equal) can also be used for loop control as in Table 1-12. Two bytes are specified in the operand field of the instruction. The jump is executed only if the two bytes are not equal. In the example of Figure 12, the two bytes were the data in R1 and the constant 2AH. The initial data in R1 was 2EH. Every time the loop was executed, R1 was decremented, and the looping was to continue until the R1 data reached 2AH.

Another application of this instruction is in "greater than, less than" comparisons. The two bytes in the operand field are taken as unsigned integers. If the first is less than the second, then the Carry bit is set (1). If the first is greater than or equal to the second, then the Carry bit is cleared.

# 1.10 Read-Modify-Write Instruction Features

See Section 2.5.4, page 76.

# 1.11 Instruction Set Summary

| Mnemon  | ic                | Description                                  | Byte | Oscillator<br>Period |

|---------|-------------------|----------------------------------------------|------|----------------------|

| ARITHMI | TIC OPERATIONS    | <b>S</b>                                     |      |                      |

| ADD     | A,R <sub>n</sub>  | Add register to Accumulator                  | 1    | 12                   |

| ADD     | A,direct          | Add direct byte to Accumulator               | 2    | 12                   |

| ADD     | A,@R <sub>i</sub> | Add indirect RAM to Accumulator              | 1    | 12                   |

| ADD     | A,#data           | Add immediate data to Accumulator            | 2    | 12                   |

| ADDC    | A,R <sub>n</sub>  | Add register to Accumulator with Carry       | 1    | 12                   |

| ADDC    | A,direct          | Add direct byte to Accumulator with Carry    | 2    | 12                   |

| ADDC    | A,@R <sub>i</sub> | Add indirect RAM to Accumulator with Carry   | 1    | 12                   |

| ADDC    | A,#data           | Add immediate data to Acc with Carry         | 2    | 12                   |

| SUBB    | A,R <sub>n</sub>  | Subtract Register from Acc with borrow       | 1    | 12                   |

| SUBB    | A,direct          | Subtract direct byte from Acc with borrow    | 2    | 12                   |

| SUBB    | A,@R <sub>i</sub> | Subtract indirect RAM from ACC with borrow   | 1    | 12                   |

| SUBB    | A,#data           | Subtract immediate data from Acc with borrow | 2    | 12                   |

| INC     | A                 | Increment Accumulator                        | 1    | 12                   |

| INC     | R <sub>n</sub>    | Increment register                           | 1    | 12                   |

| INC     | direct            | Increment direct byte                        | 2    | 12                   |

| INC     | @R <sub>i</sub>   | Increment direct RAM                         | 1    | 12                   |

| DEC     | A                 | Decrement Accumulator                        | 1    | 12                   |

| DEC     | R <sub>n</sub>    | Decrement Register                           | 1    | 12                   |

| DEC     | direct            | Decrement direct byte                        | 2    | 12                   |

| DEC     | @R <sub>i</sub>   | Decrement indirect RAM                       | 1    | 12                   |

| INC     | DPTR              | Increment Data Pointer                       | 1    | 24                   |

| MUL     | AB                | Multiply A & B                               | 1    | 48                   |

| DIV     | AB                | Divide A by B                                | 1    | 48                   |

| DA      | A                 | Decimal Adjust Accumulator                   | 1    | 12                   |

Note: 1. All mnemonics copyrighted © Intel Corp., 1980.

| Mnemon  | ic                | Description                     | Byte | Oscillator<br>Period |

|---------|-------------------|---------------------------------|------|----------------------|

| LOGICAI | OPERATIONS        |                                 |      |                      |

| ANL     | A,R <sub>n</sub>  | AND Register to Accumulator     | 1    | 12                   |

| ANL     | A,direct          | AND direct byte to Accumulator  | 2    | 12                   |

| ANL     | A,@R <sub>i</sub> | AND indirect RAM to Accumulator | 1    | 12                   |

| Mnemoni  | C                      | Description                                | Byte | Oscillator<br>Period |

|----------|------------------------|--------------------------------------------|------|----------------------|

| ANL      | A,#data                | AND immediate data to Accumulator          | 2    | 12                   |

| ANL      | direct,A               | AND Accumulator to direct byte             | 2    | 12                   |

| ANL      | direct,#data           | AND immediate data to direct byte          | 3    | 24                   |

| ORL      | A,R <sub>n</sub>       | OR register to Accumulator                 | 1    | 12                   |

| ORL      | A,direct               | OR direct byte to Accumulator              | 2    | 12                   |

| ORL      | A,@R <sub>i</sub>      | OR indirect RAM to Accumulator             | 1    | 12                   |

| ORL      | A,#data                | OR immediate data to Accumulator           | 2    | 12                   |

| ORL      | direct,A               | OR Accumulator to direct byte              | 2    | 12                   |

| ORL      | direct,#data           | OR immediate data to direct byte           | 3    | 24                   |

| XRL      | A,R <sub>n</sub>       | Exclusive-OR register to Accumulator       | 1    | 12                   |

| XRL      | A,direct               | Exclusive-OR direct byte to Accumulator    | 2    | 12                   |

| XRL      | A,@R <sub>i</sub>      | Exclusive-OR indirect RAM to Accumulator   | 1    | 12                   |

| XRL      | A,#data                | Exclusive-OR immediate data to Accumulator | 2    | 12                   |

| XRL      | direct,A               | Exclusive-OR Accumulator to direct byte    | 2    | 12                   |

| XRL      | direct,#data           | Exclusive-OR immediate data to direct byte | 3    | 24                   |

| CLR      | A                      | Clear Accumulator                          | 1    | 12                   |

| CPL      | A                      | Complement Accumulator                     | 1    | 12                   |

| RL       | A                      | Rotate Accumulator Left                    | 1    | 12                   |

| RLC      | А                      | Rotate Accumulator Left through the Carry  | 1    | 12                   |

| LOGICAL  | OPERATIONS (continue   | ed)                                        |      |                      |

| RR       | A                      | Rotate Accumulator Right                   | 1    | 12                   |

| RRC      | А                      | Rotate Accumulator Right through the Carry | 1    | 12                   |

| SWAP     | A                      | Swap nibbles within the Accumulator        | 1    | 12                   |

| DATA TRA | ANSFER                 |                                            |      |                      |

| MOV      | A,R <sub>n</sub>       | Move register to Accumulator               | 1    | 12                   |

| MOV      | A,direct               | Move direct byte to Accumulator            | 2    | 12                   |

| MOV      | A,@R <sub>i</sub>      | Move indirect RAM to Accumulator           | 1    | 12                   |

| MOV      | A,#data                | Move immediate data to Accumulator         | 2    | 12                   |

| MOV      | R <sub>n</sub> ,A      | Move Accumulator to register               | 1    | 12                   |

| MOV      | R <sub>n</sub> ,direct | Move direct byte to register               | 2    | 24                   |

| MOV      | R <sub>n</sub> ,#data  | Move immediate data to register            | 2    | 12                   |

| MOV      | direct,A               | Move Accumulator to direct byte            | 2    | 12                   |

| MOV      | direct,R <sub>n</sub>  | Move register to direct byte               | 2    | 24                   |

| MOV      | direct,direct          | Move direct byte to direct                 | 3    | 24                   |

| MOV      | direct,@R <sub>i</sub> | Move indirect RAM to direct byte           | 2    | 24                   |

| Mnemoni | С                       | Description                                    | Byte | Oscillator<br>Period |

|---------|-------------------------|------------------------------------------------|------|----------------------|

| MOV     | direct,#data            | Move immediate data to direct byte             | 3    | 24                   |

| MOV     | @R <sub>i</sub> ,A      | Move Accumulator to indirect RAM               | 1    | 12                   |

| MOV     | @R <sub>i</sub> ,direct | Move direct byte to indirect RAM               | 2    | 24                   |

| MOV     | @R <sub>i</sub> ,#data  | Move immediate data to indirect RAM            | 2    | 12                   |

| MOV     | DPTR,#data16            | Load Data Pointer with a 16-bit constant       | 3    | 24                   |

| MOVC    | A,@A+DPTR               | Move Code byte relative to DPTR to Acc         | 1    | 24                   |

| MOVC    | A,@A+PC                 | Move Code byte relative to PC to Acc           | 1    | 24                   |

| MOVX    | A,@R <sub>i</sub>       | Move External RAM (8-bit addr) to Acc          | 1    | 24                   |

| DATA TR | ANSFER (continued)      |                                                |      |                      |

| MOVX    | A,@DPTR                 | Move Exernal RAM (16-bit addr) to Acc          | 1    | 24                   |

| MOVX    | @R <sub>i</sub> ,A      | Move Acc to External RAM (8-bit addr)          | 1    | 24                   |

| MOVX    | @DPTR,A                 | Move Acc to External RAM (16-bit addr)         | 1    | 24                   |

| PUSH    | direct                  | Push direct byte onto stack                    | 2    | 24                   |

| POP     | direct                  | Pop direct byte from stack                     | 2    | 24                   |

| XCH     | A,R <sub>n</sub>        | Exchange register with Accumulator             | 1    | 12                   |

| XCH     | A,direct                | Exchange direct byte with Accumulator          | 2    | 12                   |

| XCH     | A,@R <sub>i</sub>       | Exchange indirect RAM with Accumulator         | 1    | 12                   |

| XCHD    | A,@R <sub>i</sub>       | Exchange low-order Digit indirect RAM with Acc | 1    | 12                   |

| BOOLEA  | N VARIABLE MANIPU       | ILATION                                        |      |                      |

| CLR     | С                       | Clear Carry                                    | 1    | 12                   |

| CLR     | bit                     | Clear direct bit                               | 2    | 12                   |

| SETB    | С                       | Set Carry                                      | 1    | 12                   |

| SETB    | bit                     | Set direct bit                                 | 2    | 12                   |

| CPL     | С                       | Complement Carry                               | 1    | 12                   |

| CPL     | bit                     | Complement direct bit                          | 2    | 12                   |

| ANL     | C,bit                   | AND direct bit to CARRY                        | 2    | 24                   |

| ANL     | C,/bit                  | AND complement of direct bit to Carry          | 2    | 24                   |

| ORL     | C,bit                   | OR direct bit to Carry                         | 2    | 24                   |

| ORL     | C,/bit                  | OR complement of direct bit to Carry           | 2    | 24                   |

| MOV     | C,bit                   | Move direct bit to Carry                       | 2    | 12                   |

| MOV     | bit,C                   | Move Carry to direct bit                       | 2    | 24                   |

| JC      | rel                     | Jump if Carry is set                           | 2    | 24                   |

| JNC     | rel                     | Jump if Carry not set                          | 2    | 24                   |

| Mnemoni | С                          | Description                                         | Byte | Oscillator<br>Period |

|---------|----------------------------|-----------------------------------------------------|------|----------------------|

| JB      | bit,rel                    | Jump if direct Bit is set                           | 3    | 24                   |

| JNB     | bit,rel                    | Jump if direct Bit is Not set                       | 3    | 24                   |

| JBC     | bit,rel                    | Jump if direct Bit is set & clear bit               | 3    | 24                   |

| PROGRA  | M BRANCHING                |                                                     |      |                      |

| ACALL   | addr11                     | Absolute Subroutine Call                            | 2    | 24                   |

| LCALL   | addr16                     | Long Subroutine Call                                | 3    | 24                   |

| RET     |                            | Return from Subroutine                              | 1    | 24                   |

| RETI    |                            | Return from interrupt                               | 1    | 24                   |

| AJMP    | addr11                     | Absolute Jump                                       | 2    | 24                   |

| LJMP    | addr16                     | Long Jump                                           | 3    | 24                   |

| SJMP    | rel                        | Short Jump (relative addr)                          | 2    | 24                   |

| JMP     | @A+DPTR                    | Jump indirect relative to the DPTR                  | 1    | 24                   |

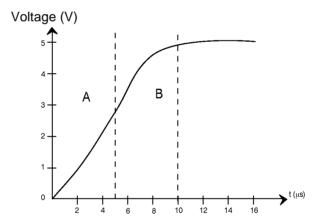

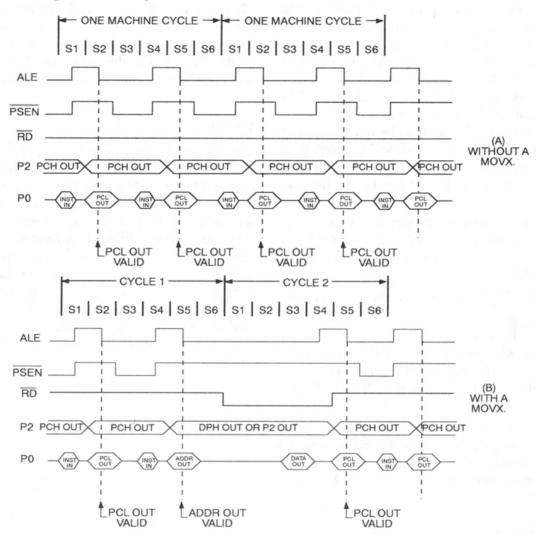

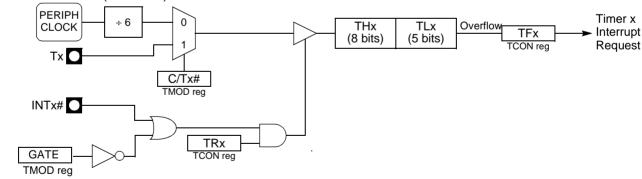

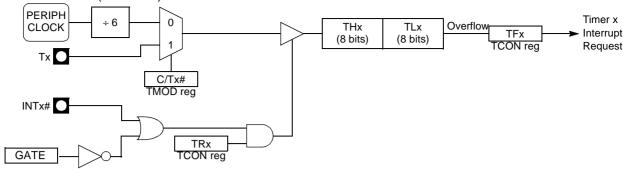

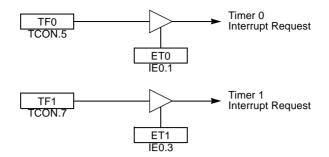

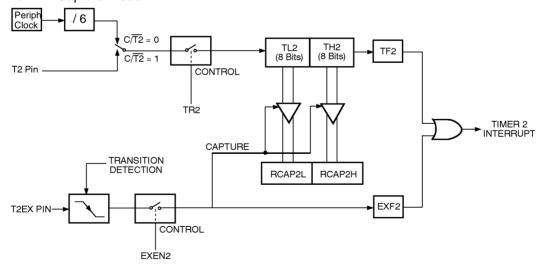

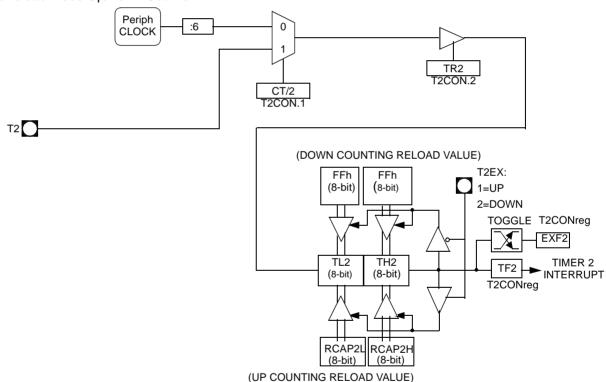

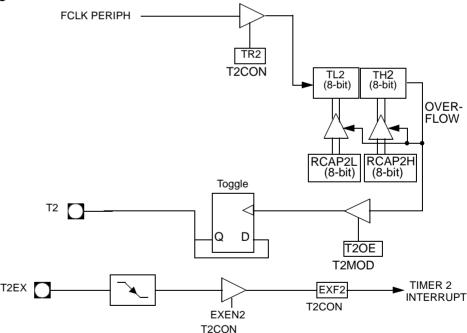

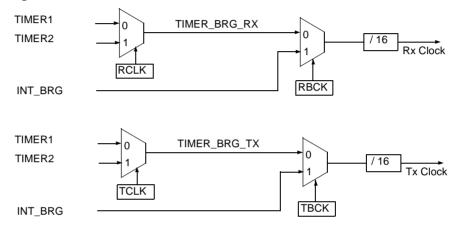

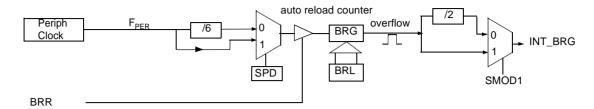

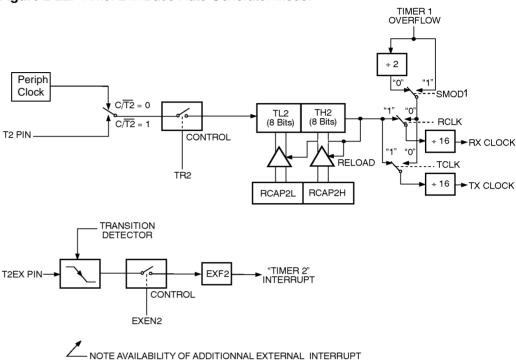

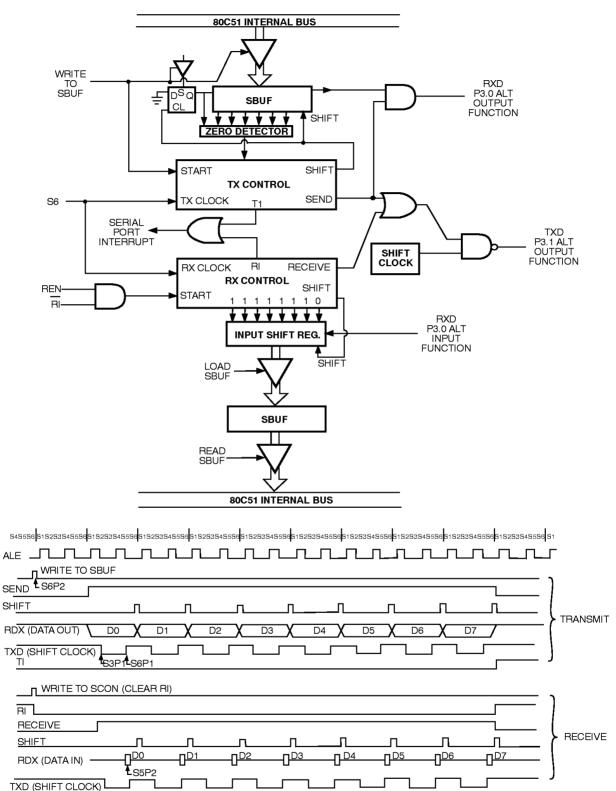

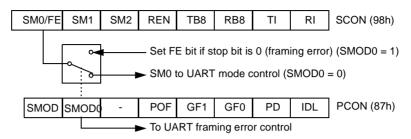

| JZ      | rel                        | Jump if Accumulator is Zero                         | 2    | 24                   |